THIS GUIDE IS STILL WORK IN PROGRESS AND MIGHT CONTAIN WRONG INFORMATION

Prerequisites:

This guide uses K-maps and state machines, which are techniques described by these guide: K-map and State Machines -or- How to solve the maze with 2 gates. So you might want to check them out before you start.

Introduction[edit | edit source]

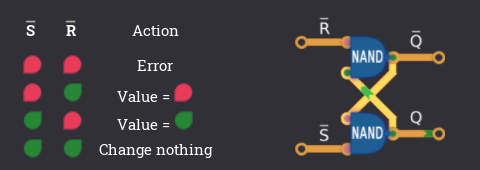

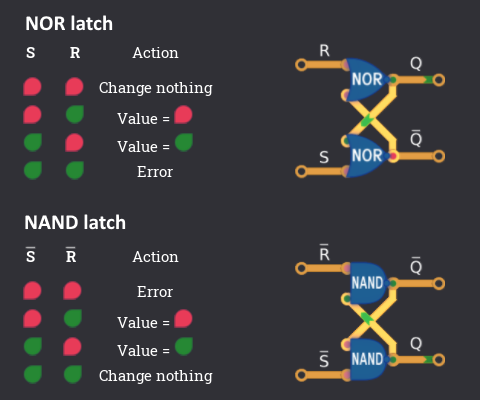

Usually the RS-Latch (R=Reset, S=Set) (in the NOR and NAND variant) is introduced as an 'existing' circuit with a litte table that describes the behaviour:

The important state is ![]()

![]() where the current value keeps the same and is saved! Therefore we can now build circuits that can save values and implement behaviour based on these previously saved values.

where the current value keeps the same and is saved! Therefore we can now build circuits that can save values and implement behaviour based on these previously saved values.

Alright that's it! Everything is clear and we can go on with life...

Except it's not! Nothing is clear!

There are so many open questions:

- What even is a latch?

- I heard it is also called a flip-flop?! What's the difference?

- Why is there an error state?

- What happens if i go into the error state anyways?

- Is there a way that I can come up with this circuit by myself?

- There is also a NAND latch explained in the manual, is that the same?

- Is that supposed to be a delay line? What is the connection?

- What about other latches and flip-flops? Like JK or T and other random letters?

These are all valid questions, that will be answered (in some way or another)!

What do we want to achieve?[edit | edit source]

Let's pretent we start with nothing, but know about techniques to design circuits like K-maps and state machines.

Side note: State machines already use D-Flip-flops to delay values internally, so one could argue that the whole explanation is kinda circular, but we only use that delay in an abstract way - until we get rid of it

The whole point of latches and flip-flops is, that we want to build a circuit which behaviour is not only based on the current input values, but also on the things that happened before. So the behaviour is described by not just a combination of current input values (Combinational logic), but a sequence of input values over time (Sequential logic).

So what do we want to do?

1: We have 2 input values S and R and one output Q 2: If S is, we want to set the output to

3: If R is

, we want to reset the output back to

4: If neither S nor R is

, the output keeps the signal that it already has

Side note: A latch has 2 outputs, but we will get to that later.

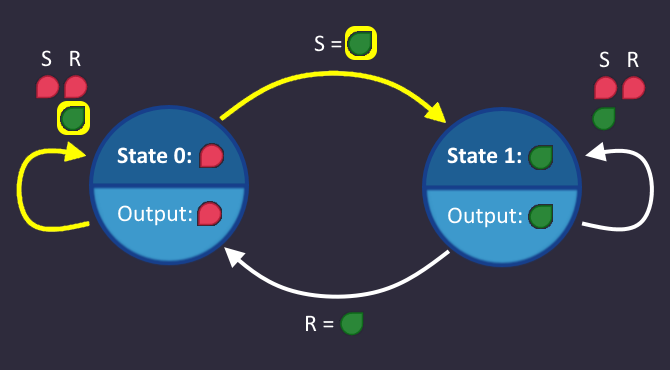

This is the simplest sequential logic that we can build. You can see the squential part whenever neither R and S in ![]() , because then the ouput can be anything - depending on whether S or R was

, because then the ouput can be anything - depending on whether S or R was ![]() before in time. And whenever we have sequential logic, we can build a circuit by using state machines! So let's see how it looks like:

before in time. And whenever we have sequential logic, we can build a circuit by using state machines! So let's see how it looks like:

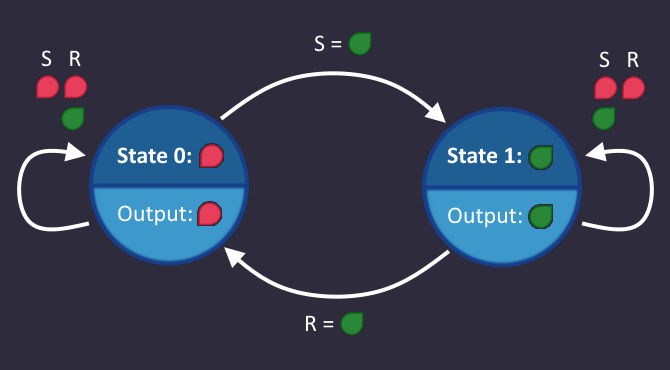

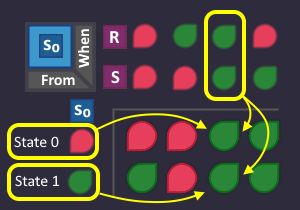

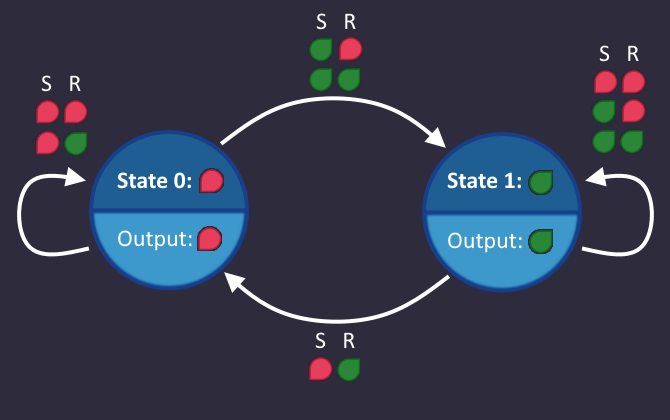

Doesn't look so bad... let's build it!

We have a single state variable ![]() , which is

, which is ![]() in State 0 and

in State 0 and ![]() in State 1. The output is identical to that value. Let's see what circumstances lead to the variable

in State 1. The output is identical to that value. Let's see what circumstances lead to the variable ![]() beeing

beeing ![]() .

.

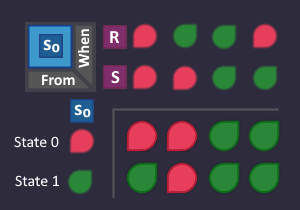

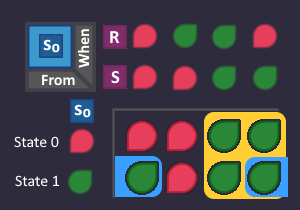

Each condition on an arrow is a bit in a K-map, which we can use to build the circuit. So each condition, that we highlighted in our state machine is now turned to ![]() in our K-map:

in our K-map:

So far so good. Since we have a filled K-map now, we can draw blocks and derive the circuit!

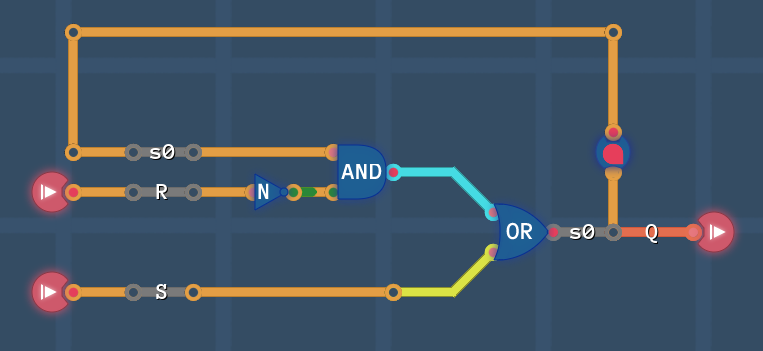

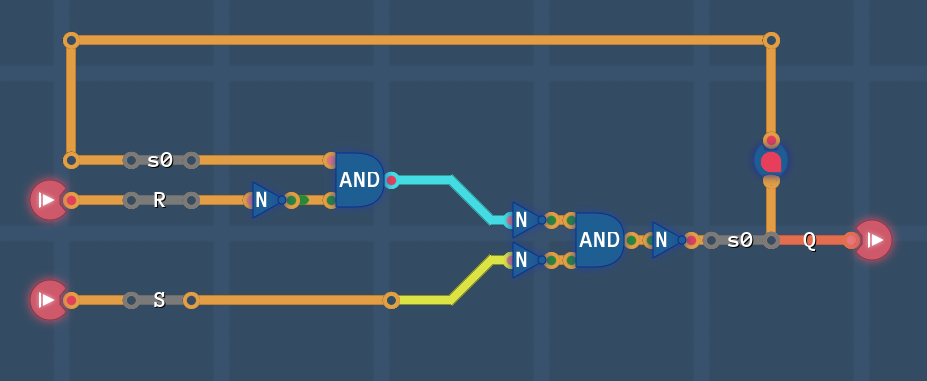

Just for fun: let's apply De Morgan's law to the OR gate and see what happens:

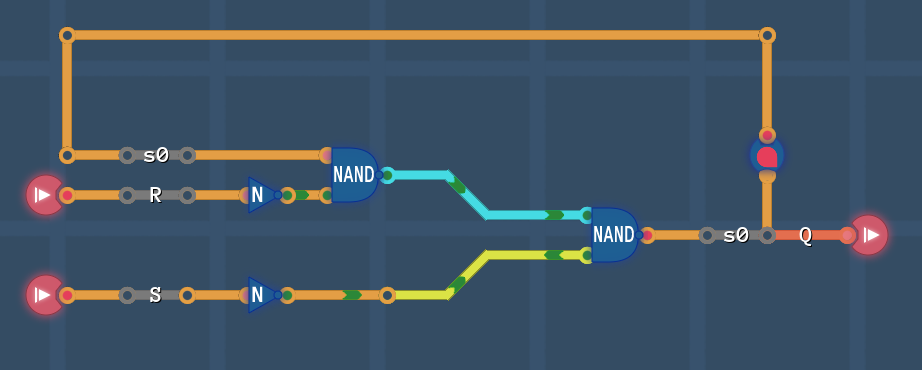

Combine NOTs and ANDs into NANDs

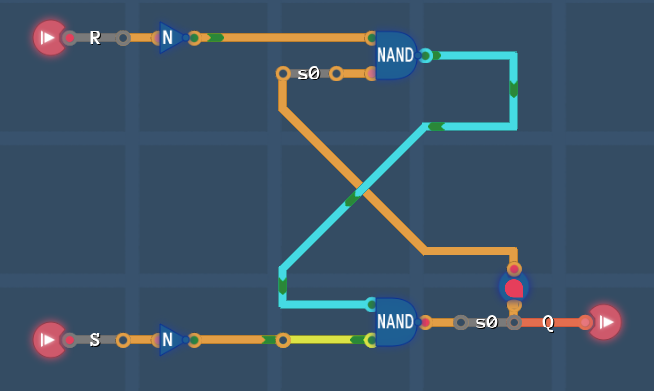

And now reorder it a bit

Looks familiar?

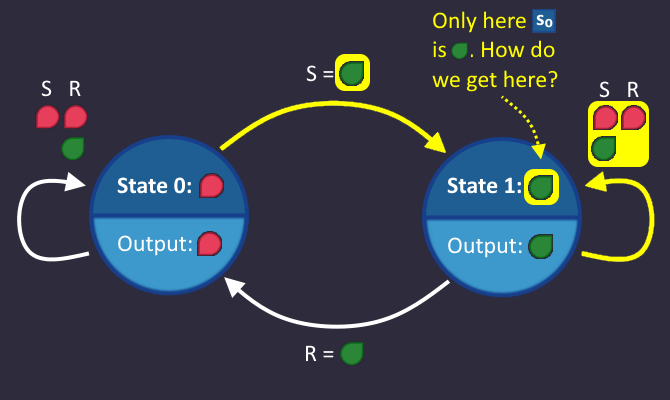

We're on the right track (but not quite there, yet)! First of all, let's analyze what happens if both inputs are ![]() . We can either do that by looking at the state machine, but the truth lies in the K-maps that we turned into our circuit.

. We can either do that by looking at the state machine, but the truth lies in the K-maps that we turned into our circuit.

Notice: When both inputs S and R are ![]() , we always switch to state 1.

, we always switch to state 1.

This does not line up with our state machine!

The state machine contains contradictions!

If we are in state 0, and both inputs are ![]() , there are two arrows, that we can take: we can either stay in state 0 (because R is

, there are two arrows, that we can take: we can either stay in state 0 (because R is ![]() ), or we can go to state 1 (because S is

), or we can go to state 1 (because S is ![]() ).

).

The same applies to state 1. Again there are two arrows that we can take, if both inputs are ![]() :

:

What really happens in these cases is defined by our K-map (our circuit) that we build. And as you have seen above in our K-map, it always goes to ![]() - it favors state 1! So now we have to update our state machine and get rid of the contradictions, so that it matches the K-maps.

- it favors state 1! So now we have to update our state machine and get rid of the contradictions, so that it matches the K-maps.

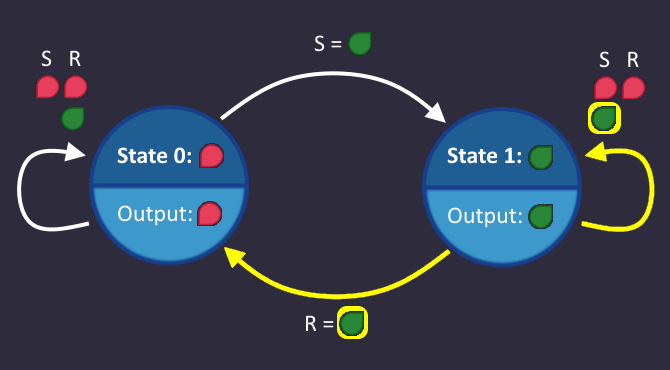

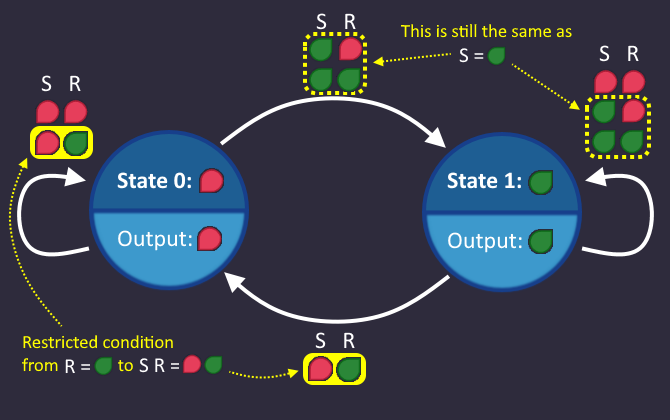

Let's modify the arrows and get rid of the contradictions:

State 0: If R is ![]() , then we stay in state 0 only if S is

, then we stay in state 0 only if S is ![]() . Because if both are

. Because if both are ![]() , we go to state 1.

State 1: If R is

, we go to state 1.

State 1: If R is ![]() , then we go to state 0 only if S is

, then we go to state 0 only if S is ![]() . Because if both are

. Because if both are ![]() , we stay in state 1.

, we stay in state 1.

Now our state machine is nice and clean and describes exactly what we have build.

One thing is strange, though: The circuit contains 2 NAND gates, which are build up symmetrically. However the state machine is NOT symmetrical - it clearly favors state 1! Shouldn't they be both symmetrical?

Yes. (That's another clue, that we are still not finnished, yet)