w:c:strategywiki>Henke37 (Switch to Y/N templates) |

(Added infobox) |

||

| (3 intermediate revisions by the same user not shown) | |||

| Line 1: | Line 1: | ||

{{Header Nav|game=Turing Complete}} | {{Header Nav|game=Turing Complete}} | ||

{{Infobox level | |||

| section = Basic Logic | |||

| type = Component | |||

| prerequisite1 = Second Tick | |||

| unlocks-level1 = Bigger OR Gate | |||

| unlocks-level2 = Bigger AND Gate | |||

| unlocks-component1 = XOR | |||

| unlocks-page1 = Truth tables | |||

| unlocks-page2 = Universal gates | |||

| unlocks-feature1 = Online profile | |||

| scored = Yes | |||

| highscore = 7 | |||

| api-enum-id = xor_gate | |||

| api-enum-number = 4 | |||

}} | |||

This level has you create the XOR Gate. It is like the OR gate except that it outputs false if both inputs are true. | This level has you create the XOR Gate. It is like the OR gate except that it outputs false if both inputs are true. | ||

| Line 9: | Line 25: | ||

}} | }} | ||

{| {{ | {| {{TruthTable}} | ||

|+ XOR Gate Truth Table | |+ XOR Gate Truth Table | ||

|- | |- | ||

! Input | ! Input 1 !! Input 2 !! Output | ||

|- | |- | ||

| {{ | | {{Off t}}|| {{Off t}}|| {{Off t}} | ||

|- | |- | ||

| {{ | | {{Off t}}|| {{On t}}|| {{On t}} | ||

|- | |- | ||

| {{ | | {{On t}}|| {{Off t}}|| {{On t}} | ||

|- | |- | ||

| {{ | | {{On t}}|| {{On t}}|| {{Off t}} | ||

|} | |} | ||

Latest revision as of 07:26, 2 September 2024

| Section | Basic Logic |

|---|---|

| Type | Component |

| Prerequisite | Second Tick |

| Unlocks | Bigger OR Gate Bigger AND Gate |

| XOR | |

| Truth tables Universal gates | |

| Online profile | |

| Scored | Yes |

| High score | 7 |

| API | xor_gate (4) |

This level has you create the XOR Gate. It is like the OR gate except that it outputs false if both inputs are true.

| Input 1 | Input 2 | Output |

|---|---|---|

0 |

0 |

0

|

0 |

1 |

1

|

1 |

0 |

1

|

1 |

1 |

0

|

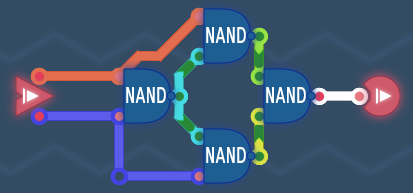

The solution to this level requires more effort than just placing down a single NAND gate and some inverters.

The simplest solution, which is also required for the achievement, is to place four NAND gates. The first one has the input pins as the input, while the second and third have one of the input pins and the output of the first gate as the inputs. The final gate has the inputs hooked up to the second and third gate.